FPGA Learning Series: 5. Blocking assignments and non-blocking assignments

design background:

Blocking (=) and non-blocking (<=) have always been issues discussed in our FPGAs. Senior scholars are talking about whether the assignment should occur at the rising or falling edge or where we are looking at in simulations. It is accurate, but this is not known in the time circuit. Today we will learn the difference between blocking and non-blocking. We do not study where they happened, where and when the discussion occurred.

Â

Design principle : Â

Blocking: After the "right-style calculation" and "left-style update" in this sentence are completely completed, the next statement is executed;

Non-blocking: The execution of the current statement does not block the execution of the next statement.

Â

Let's take a look at the blocked code below

0 Â Module study_4 ( clk , rst_n , d , q );

1 Â // Input and output ports

2 Â Input clk ;

3 Â Input rst_n ;

4  Input  [ 1 : 0 ] d ;

5  Output  Reg  [ 1 : 0 ] q ;

6 Â

7  Reg  [ 1 : 0 ] q1 ;     // define a register

8 Â

9  Always  @  ( posedge clk )

10 begin

11 if (! rst_n ) // reset to initial value of the register output

12 begin

13 q1 = Â 0 ;

14 q = Â 0 ;

15 end

16 else //The blocking statement is assigned

17 begin

18 q1 = d ;

19 q = q1 ;

20 end

21 end

twenty two

twenty three  Endmodule Â

The always statement block is sensitive to the rising edge of Clk. When the transition of Clk 0 to 1 occurs, the always statement is executed.

All the statements in the begin...end block are executed sequentially, and the most critical is that the block assignment is executed after the “right calculation†and “left update†in this sentence are completely completed. of.

In the above code, on the 18th row, when the rising edge comes first, the value of d is given to q1, and then the next rising edge assigns q1 to q.

Our test file is as follows:

0  `timescale  1ns  /  1ps

1 Â

2 Â Module tb ;

3 Â

4 Â Reg clk ;

5 Â Reg rst_n ;

6  Reg  [ 1 : 0 ] d ;

7  Wire  [ 1 : 0 ] q ;

8 Â

9  Initial  Begin

10 clk = Â 1 ;

11 rst_n = Â 0 ;

12 d = Â 0 ;

13

14 # 200.1 rst_n = Â 1 ;

15

16 # 100 d = Â 2 ;

17 # 100 d = Â 0 ;

18

19 end

20

21 always  # 10 clk =  ~ clk ;

twenty two

23 study_4 dut (

24 . clk ( clk ), Â

25 . rst_n ( rst_n ),

26 . d ( d ),

27 . q ( q )

28 );

29

30 Â Endmodule Â

Â

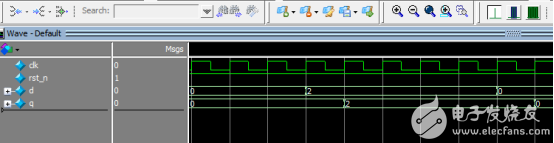

Put the map as follows:

Â

Â

Â

We can clearly see that the first rising edge of the register q is 0, the second rising edge q is 2 , then look at the non-blocking assignment.

The so-called non-blocking assignment, as the name suggests, means that the execution of the current statement will not block the execution of the next statement.

Non-blocking code is as follows:

0 Â Module study_4 ( clk , rst_n , d , q );

1 Â

2 Â Input clk ;

3 Â Input rst_n ;

4  Input  [ 1 : 0 ] d ;

5  Output  Reg  [ 1 : 0 ] q ;

6 Â

7  Reg  [ 1 : 0 ] q1 ;

8 Â

9  Always  @  ( posedge clk )

10 begin

11 if (! Rst_n) // reset to a non-blocking initial value register output

12 begin

13 q1 <= Â 0 ;

14 q <= Â 0 ;

15 end

16 else // non-blocking assignment statement

17 begin

18 q1 <= d ;

19 q <= q1 ;

20 end

21 end

twenty two

twenty three  Endmodule Â

Â

Non-blocking is performed after 18 rows. The value of d is given to q1 on the 18th row, but it is not immediately given to the past, but is waited until the rise, and the same row of 19 is executed on the rising edge, giving the q1 value to q. We must understand that the value at this time is the old value of q1, and then the same value is given to the past after the arrival of the rising edge.

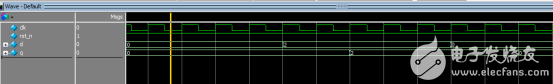

We use the same simulation files for the two modules. I will not show them here. We can directly look at the simulation diagram, as follows:

Â

Â

Â

We can clearly see that at the first rising edge, the value of d is 2, the execution of 18 lines is not directly assigned, the value is passed when the rising edge comes, and the same is performed in the following, then we You can see the same figure as our analysis.

LED Lighting Aluminum Alloy Die Casting

Led Lighting Aluminum Alloy Die Casting,Oem Aluminium Alloy Die,Led Zinc Die Casting,Aluminium Led Light Housing

Dongguan Metalwork Technology Co., LTD. , https://www.dgdiecastpro.com